# 遥感相机中影响 FPGA 配置的因素分析

肖 龙 贺强民

(北京空间机电研究所 北京 100094)

摘 要: FPGA 器件在空间遥感相机中应用越来越广泛,基于 SRAM 的 FPGA 必须配备 PROM 芯片,用以存放 FPGA 的编程数据,每次上电都需要重新加载配置,但受各种因素的影响,程序加载配置并不是每次都能成功。阐述 了有关 FPGA 的配置过程,分析了影响配置的各个因素,并提出相应的设计优化措施。出现配置失败的电路,经设计优化后未曾出现配置失败。作为航天任务,遥感相机中绝不应出现 FPGA 配置失败的状态,为了提高上电配置的可靠性,提出了监测多个 I/O 信号电路方案,利用可靠性高的反熔丝 FPGA 来监测需要配置的 FPGA,经数千次加载试验,FPGA 配置成功率为 100%,该方案对遥感相机更好地应用 FPGA 具有一定的参考价值。

关键词: FPGA;遥感相机;配置;可靠性

中图分类号: V19 文献标识码: A 国家标准学科分类代码: 510.1010

# Analysis of factors affecting FPGA configuration in remote camera

Xiao Long He Qiangmin (Beijing Institute of Space Mechanics & Electricity, Beijing 100094, China)

Abstract: FPGA devices are more widely used in space remote sensing cameras. FPGA based on SRAM must be equipped with corresponding prom chips for storing FPGA programming data. The configuration is reloaded after power on. However, the configuration does not always succeed for it is easily affected by various factors. This paper describes FPGA configuration process, analyze the various factors affecting the configuration and make recommendations for design optimization. The Configuration circuits do not fail in hundreds of configuration tests after optimization. As space missions, FPGA configuration failure in remote sensing camera should never occur, in order to improve the reliability of power-on configuration, this paper presents a number of IO signal monitoring strategies. The use of high reliability anti-fuse FPGA which monitor the FPGA needed to be configured, can guarantee FPGA configuration almost 100% success. It has significant reference value in application of remote sensing cameras.

Keywords: FPGA; remote sensing camera; configuration; reliability

# 1 引 言

现场可编程门阵列(field programmable gate array, FPGA)器件,拥有高度的灵活性、丰富的 I/O 资源和内嵌模块等优势,在空间遥感相机中应用越来越广泛。FPGA 的生产工艺主要有 SRAM 结构、反熔丝结构以及 Flash 结构。基于 SRAM 工艺来实现的 FPGA,由于掉电后 SRAM 会失去所有配置数据,因此基于 SRAM 的 FPGA 必须配备相应的 PROM 芯片,用以存放 FPGA 的编程数据,每次上电都需要重新加载<sup>□</sup>,但加载的过程容易受到外界干扰而导致程序配置失败。

在遥感相机里,作为主处理器的 FPGA 器件,绝对不容许上电加载配置失败。FPGA 厂商在发布的数据手册和勘误文档里,提到可能导致程序配置失败的因素,但是说明

不够明确详细。国内外探讨 FPGA 配置失败的文献很少,且大多从外部因素分析,例如环境温度、信号完整性、供电电压等,而缺乏对于配置信号等内在因素的分析。

就 FPGA 芯片在配置中出现的问题展开讨论,结合数据 文档,联系工程实际,从配置信号方面更深入地分析各种因素, 对配置电路进行了相应的优化设计,并提出了一种提高 FPGA 配置可靠性的可行性方案,可提高 FPGA 配置成功率。

### 2 FPGA 上电配置过程的工作原理

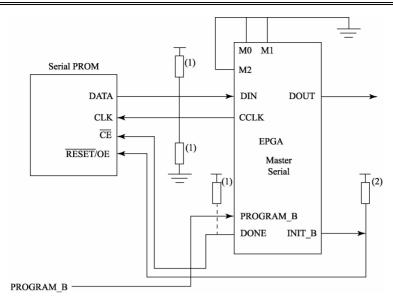

FPGA 的配置模式以主串模式为例, FPGA 驱动 CCLK 引脚,每个 CCLK 周期载入一个 bit 的方式配置。主串模式使用器件较少,简单灵活可靠,缺点是串行配置时间较长。如图 1 所示 FPGA 主串模式配置。

图 1 主动串行配置

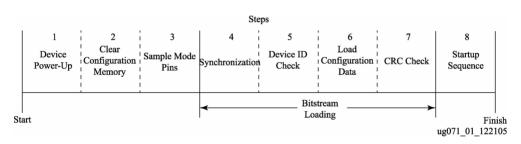

FPGA 配置过程[2]分为设置、比特流下载和启动 3 个 步骤。如图 2 所示其配置过程。

图 2 配置过程

#### 1)设置

设置过程又分3个步骤

- ①上电。Vcc-config、Vccaux 和 Vccint 引脚提供合适电源,电源电压达到要求后便会自动初始化;

- ②清空配置存储器。只要芯片上电,配置存储器就清空:

- ③取样模式引脚。当 INIT 引脚变为高电平,芯片开始取样输入引脚配置数据。

- 2)比特流下载分为4个步骤

- ①同步,在配置数据帧下载之前,同步字必须先送到 配置逻辑。同步字告知芯片即将到来的配置数据和将配 置数据和内部配置逻辑进行排列。

- ②芯片 ID 检查。在同步之后,必须通过芯片 ID 检查才能进行配置数据下载。这将保证在芯片不被错误配置为其他芯片的配置数据。

- ③配置数据帧下载。

- ④CRC 校验。配置数据帧下载完成后,就用期望 CRC 值来进行 CRC 检查。如果 CRC 值与比特流中期望的 CRC

值不匹配,则拉低 INIT 引脚并中止配置过程。

- 3)启动(START-UP),该步骤是由配置状态过渡到用户状态的过程,在START-UP完成后,FPGA便可实现用户编程功能。在START-UP阶段中FPGA进行的如下操作:

- ①将 DONE 信号置高;

- ②全局写允许信号 GWE 置低电平,所有内部 RAM 有效;

- ③全局三态信号 GTS 置低,器件的所有 IO 引脚将会 从配置时的三态切换到用户设置的状态:

- ④启动结束。

配置的过程是 FPGA 厂商固化在芯片中的程序决定的,外部无法干预该过程,但用户可以利用设备测试配置信号,观察配置信号的时序和质量。配置失败的直接表象为 DONE信号没有变为高电平,而配置失败与 FPGA 配置电路的设计存在必然的联系。下节将从每个涉及配置的因素,结合实际遇到问题进行分析讨论,并提出相应的解决措施。

# 3 影响配置过程的因素分析

在 FPGA 上电配置过程,工作的是电源,RROM 以及 FPGA 配置信号,所以配置是否成功,与 PROM、电源和配

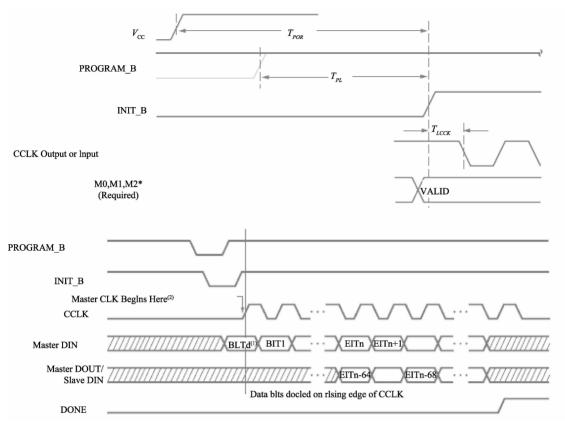

置信号有着必然的关系。从经历过的诸多 FPGA 配置失败案例中,作者总结了以下几个方面。图 3 为配置时的时序关系。

图 3 上电配置时序

#### 3.1 FPGA 供电

#### 1)上电顺序

以前某型号的 FPGA 明确要求 Vccint (核电)的电源上升时间如果超过 10 ms,则要求 Vccint 先与 Vcco(IO电)和 Vccaux(辅助电)加电。如果违反此原则,可能会导致配置失败。在对该型号的 FPGA 配置时发现,在核电慢于 I/O 电时,出现一定概率的配置失败情况。而最新的 FPGA 没有提出上电顺序的要求,作者在某新一代 FPGA 试验中,改变上电顺序若干次,没有发现配置失败的情况。但建议按照 Vccint、Vccaux、Vcco 的顺序加电,改变顺序后各个电源的启动电流会发生变化,反过来可能会影响供电电源。如果供电电源的电流不足,也可导致配置失败。

#### 2)电源质量

Vccint、Vccaux、Vcco电源上尽可能加滤波电容,保证电源纹波尽可能小。对于大容值钽电容数量,小容值陶瓷电容种类和数量都有推荐,建议按照 PCB 设计规范设计。电源完整性非常重要[3],电源纹波过大或者易受干扰,可

能在配置的过程中影响加载数据或者时钟,使得 CRC 校验无法通过,导致配置失败。

#### 3.2 PROM 供电以及相关

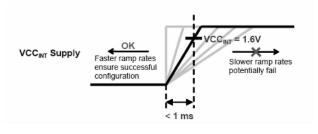

1)Flash 类型的 PROM 相关文档明确要求 PROM 供电 Vccint 必须单调,且上升时间大于 0.2 ms 并小于 50 ms,如图 4 所示。但在相关手册勘误里提到,如果 Vccint 上升时间大于 1 ms,可能存在潜在的配置失败。建议合理选择供电 LDO,输出电容,保证 Vccint 上升时间上升时间大于 0.2 ms 且小于 1 ms。

图 4 Vccint 要求

2)OTP 类型的 PROM,强烈建议系统设计时,对于断电后再次启动时,VCC 能掉电到 0V。某试验电路 VCC 3.3 V断电后,由于电源电容较多,使得 3.3 V电源下降至 300 mV 后停留很长时间,这个期间重新加电,较大概率地出现了配置失败的情况。作者在 3.3 V 电源上减小并联电阻,增加断电后的泄放电流<sup>[4]</sup>,经改造后的试验电路,加电数百次未出现配置失败。建议根据实际情况,增大断电后的泄放电流或增多泄放通路,让 RROM 电源尽快掉电到 0V。

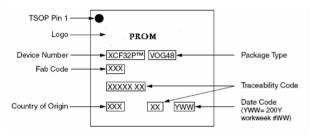

3)其他。同样型号的 PROM,如图 5 中标识"Fab Code",标识"Country of Origin"有所不同,例如"Fab Code"可能是 ART,BRT,BTT等,代表掩膜、晶圆或其他不同。其他标识"Country Origin"为原产国,可能是MYS、SGP,分别代表马来西亚、新加坡。作者曾发现同样的配置电路,使用标识"ART"的 PROM,配置没有问题,使用标识"BRT"就会出现配置问题。这种情况可能与 PROM 芯片本身,对配置信号的信号完整性要求有关系。

图 5 48 管脚 TSOP 标记

#### 3.3 PROGRAM\_B 信号

置低 PROGRAM\_B 可以重启 FPGA 配置过程, FPGA 将继续清空它的配置存储器并使 INIT 信号保持为低电平以表明配置存储器在被清空。当 PROGRAM\_B 被释放时,FPGA 将继续使 INIT 保持为低电平,直到完成清空所有的配置存储器。PROGRAM\_B 的最小的脉冲时间为 300 ns。没有最大值的限制。某试验电路中,为了过滤 PROGRAM\_B 上毛刺,让其更加平滑,在 PROGRAM\_B 管脚增加了 22  $\mu$ F 钽电容,发现配置失败且概率较大。根据实测波形。发现增加钽电容后,使得 PROGRAM\_B 信号慢于 INIT 信号,使得加载时序出现错误,进而导致配置失败。如果不能避免增加电容,建议根据 PROGRAM\_B 和 INIT 实际相位,在 PROGRAM\_B 管脚处增加少量陶瓷电容。

#### 3.4 INIT 信号

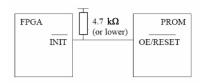

TICCK 为 INIT 变为高电平后到 CCLK 下降沿的最小时间为 500 ns,所以建议 INIT 信号的上升时间小于 500 ns,那么上拉电阻最大选择  $4.7~k\Omega$ 。如果上升时间过于缓慢,约为配置周期的  $1\%\sim5\%$ 时,会使得 PROM 内部同步出错,从而导致配置失败。如图 6~所示,INIT 信号连

接示意。

图 6 INIT 信号连接示意

# 3.5 DONE 信号

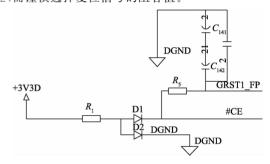

DONE 为敏感信号,作为配置完成的标志信号,一旦配置成功,该信号即变为高电平。在某些电路设计中,通常将 DONE 信号作为 FPGA 的全局复位信号[5],如果不处理得当,可能导致配置失败。如图 7 所示某电路 # CE 为DONE 信号,与 FPGA 全局复位信号 GRST1\_FP 通过  $R_s$  连接。 $R_s$  选择为 51  $\Omega$ ,会使 DONE 信号与复位信号一样上升时间过长,进而出现了配置失败。后加大  $R_s$  到 4. 7 k $\Omega$ ,DONE 信号上升沿很快建立,加电数百次再未出现配置失败。所以如果选择 DONE 作为 FPGA 软件全局复位,需谨慎选择复位信号的阻容值。

图 7 DONE 作为复位信号的电路

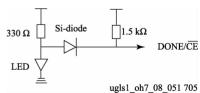

在某些电路也会利用 DONE 信号配合 LED,用来配置完成的视觉指示。由于 FPGA 管脚提供的最大电流有限,不建议直接将 LED 与 DONE 连接,因为 DONE 驱动电路不够,有可能导致 DONE 信号在中间电平停留一段时间,可能导致配置失败。建议按如图 8 所示连接。

图 8 DONE 与 LED 配合使用电路

#### 3.6 CCLK 信号

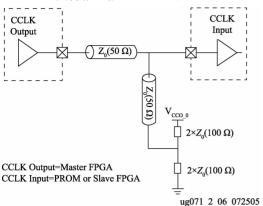

CCLK 作为配置时钟,时钟速率可达几十 MHz,相对于其他几个配置信号而言,需要重点考虑信号完整性<sup>[6]</sup>。如果时钟质量不好,可能造成数据判读出错,导致配置失败。CCLK 有以下几点需要注意:

- 1)信号特征阻抗为 50 Ω;

- 2)最好不要有分支,如果不可避免,建议不超过8 mm:

- 3) CCLK 的端接方式如图 9 所示。

图 9 CCLK 端接方式

使用多片 PROM 级联配置时<sup>[7]</sup>,作者发现源端匹配时,示波器测试波形好于图 9 的戴维南匹配,戴维南匹配下的 CCLK 过冲较大,低电平抬高几百 mV,而 CCLK 跳变沿很陡。但同样的配置电路,CCLK 波形较好的源端匹配却出现了配置失败。分析与源端匹配造成 CCLK 上升沿略缓有关,所以建议 CCLK 使用戴维南端接。

#### 4 提高配置可靠性的建议

在 3 中,作者针对每个因素给出了相应的建议和措施,曾出现配置失败的电路经改造后,加电数百次再未出现配置失败的情况。为了使 FPGA 配置可靠性更高,需要进一步的完善电路设计。对于配置失败问题,需要在最短的时间里做出判断,并重新给出配置加载信号或者重新加电。

对于遥感相机而言,作者认为以下2种方案可行。

1)较为简单的方案,就是将 DONE 信号作为遥测数据。DONE 信号为可以尝试通过缓冲器或隔离器处理后使用。在相机成像电路上电后单个或多个配置周期后,遥测到 DONE 信号未置高,判读配置失败,然后执行重加电操作。此项措施对于电路而言,改动最小,但需要考虑 DONE 信号遥测电路对 DONE 信号阻抗的影响,遥测电路可靠性、时间因素和人为因素,最主要是时间的延误,可能导致单次目标拍摄失败[8]。

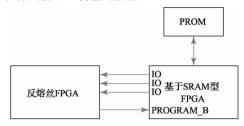

2)另一种方案比较复杂,就是增加配置监测电路,涉及软硬件。这种方案有文献提及过<sup>[3]</sup>,大多都是监测配置信号或监测 I/O,控制 PROGRAM\_B。作者选择监测FPGA 多个普通 I/O 信号,多个 I/O 可增加判读的可靠性。该方案不监测配置信号,而监测电路可能会对配置信号造成影响,因为配置信号阻抗的变化可能增加配置失败的概率。

此方案需要增加可靠性高的反熔丝 FPGA 或者 CPLD<sup>[10-12]</sup>,或看门狗,这些可编程逻辑器件不需要外部配置 就可直接工作。下面介绍该方案。反熔丝 FPGA 和基于 SRAM 型的 FPGA(以下简称主 FPGA)监测方案如图 10 所示。主 FPGA 多个普通 I/O 与反熔丝 FPGA 连接,反熔丝 FPGA 其中一个 I/O 连接主 FPGA 的 PROGRAM\_B 信号。两者同时加电,如果主 FPGA 上电配置成功,程序开始运行,主 FPGA 指定 I/O 会输出数据到反熔丝 FPGA,反熔丝 FPGA 软件判读 I/O 传输的数据。

图 10 反熔丝 FPGA 监测方案

以3个I/O连接为例,每个I/O输出时钟信号,反熔丝FPGA程序计数值设定某一个值,时间在ms即可。3个I/O中只要有一个正确,即可判断配置成功。若都不正确,即断定配置失败,然后计数器清零,输出到FPGA的PROGRAM\_B引脚输出一个时间长度大于330ns的低电平,让FPGA重新配置,然后再次检测I/O。如表1所示2种配置设计的配置试验结果,增加配置监控电路的FPGA配置成功率达到了100%。

表 1 2 种配置设计试验结果比较

| 传统配置设计 |       |    | 监控配置设计 |       |    |

|--------|-------|----|--------|-------|----|

| 组数     | 配置    | 失败 | 组数     | 配置    | 失败 |

|        | 次数    | 次数 |        | 次数    | 次数 |

| 1      | 1 000 | 1  | 1      | 1 000 | 0  |

| 2      | 1 000 | 1  | 2      | 1 000 | 0  |

| 3      | 1 000 | 2  | 3      | 1 000 | 0  |

| 4      | 1 000 | 0  | 4      | 1 000 | 0  |

| 5      | 1 000 | 0  | 5      | 1 000 | 0  |

| 6      | 1 000 | 1  | 6      | 1 000 | 0  |

| 7      | 1 000 | 2  | 7      | 1 000 | 0  |

| 8      | 1 000 | 1  | 8      | 1 000 | 0  |

| 9      | 1 000 | 0  | 9      | 1 000 | 0  |

| 10     | 1 000 | 1  | 10     | 1 000 | 0  |

#### 5 结 论

针对 FPGA 的上电配置相关因素,结合工程实际进行了一系列分析与试验,并提出了相应的设计建议,这些优化的设计提高了配置成功率,解决了实际工程中配置失败的问题。FPGA 配置要做到航天绝对成功的可靠性要求,建议对 FPGA 上电配置进行监控,提出的基于反熔丝可编

程逻辑芯片监测多个 I/O 的设计方法,可以进一步提高了FPGA 的应用可靠性,对遥感相机的 FPGA 应用具有一定的参考价值。

# 参考文献

- [1] 闰蕾,王强,房亮,等. 可编程逻辑器件在空间电子学设备中的应用[J]. 空间科学学报,2009,29(1):54-58.

- [2] 孙立波,雷加. 基于 SRAM 型 FPGA 测试技术的研究[J]. 国外电子测量技术,2011,30(5);36-40.

- [3] 石殊,吴斌,周玉梅. 高速无线芯片原型系统设计与 实现[J]. 国外电子测量技术,2012,31(2):71-75.

- [4] 蓝凤相. 论航天遥感器研制过程中的防静电[J]. 航 天返回与遥感,2001,22(2):29-33.

- [5] 成桂梅,吴雁林,苏蕾,等.基于 FPGA 的数据接口电路设计[J]. 航天返回与遥感,2005,26(4):31-36.

- [6] 蔡国发,章杰. 差分对信号完整性分析[J]. 电子测量 技术,2012,35(1):38-41.

- [7] 王典洪,周欣. 高速时序信号完整性及时钟端接问题

- 研究口[J]. 电子测量技术,2007,30(3):25-28.

- [8] 俞绍安. 卫星电源分系统可靠性设计与研究[J]. 今日电子,2009(2):90-92.

- [9] 王文华,韩双丽,张宇,等. 航天应用 FPGA 配置可靠性研究[J]. 空间科学学报,2011,31(1):106-111.

- [10] 王刚,李平,李威,等. 反熔丝的研究与应用[J]. 材料导报,2011,25(11),30-33.

- [11] 石俊霞,李佩玥,郭永飞,等. 航天遥感 TDI CCD 相 机面阵成像模式的实现[J]. 国外电子测量技术, 2014,33(5):97-101.

- [12] 冯汝鹏,徐伟,朴永杰,等. 基于 SRAM 型 FPGA 的容错性设计[J]. 电子测量技术,2014,37(10):76-80.

# 作者简介

**肖龙**,工学硕士,高级工程师,主要研究方向为航天遥感器视频电子学。

E-mail: castxiaoxiao@126. com

#### (上接第 44 页)

- [5] 王媛媛,胡爱娜. RSSI 和距离区间映射的测距方法[J]. 电子科技大学学报, 2012, 41(4):522-526.

- [7] FANG ZH, ZHAO ZH, GENG D Q, et al. RSSI variability characterization and calibration method in wireless sensor network [C]. IEEE International Conference on Information and Automation, 2010: 1532-1537.

- [8] 陈丹琪,万里冰,袁静,等. 基于快速查表的 RSSI 定位算法[J]. 微计算机信息,2009,25(15);245-247.

- [9] LI J, LIU H P. A new weighted centroid localization algorithm in coal mine wireless sensor networks[C]. Proceedings of the 3rd IEEE International Conference on Computer Research and Development, 2011;

106-109.

- [10] 韩江洪,祝满拳,马学森,等. 基于 RSSI 的极大似然与加权质心混合定位算法[J]. 电子测量与仪器学报,2013,27(10);937-943.

- [11] 张亚丽,陈名松,刘潇忆,等. 基于 DV-HOP 的 WSN 节点定位改进算法的研究[J]. 电子测量技术,2013,36(5):49-53.

- [12] 丁琳,管小卫,朱霞,等. 基于 RSSI 的集群实时定位 系统设计[J]. 国外电子测量技术,2014,33(12): 69-73.

# 作者简介

**沈田**,博士,讲师。主要研究方向为认知无线电功率 控制、物联网定位技术等。

E-mail: yezi\_sht@163.com