#### ELECTRONIC MEASUREMENT TECHNOLOGY

## 高效视频编码(HEVC)帧内预测的硬件实现方案

#### 夏正鹏 孝开宇

(南京航空航天大学自动化学院 南京 211106)

摘 要:为了满足实时性要求,提出了基于现场可编程门阵列(field-programmable gate array, FPGA)的帧内预测并行化设计架构。通过并行架构来减少运算等待时间,通过查找表简化了参考像素选取过程,通过预测运算单元来降低计算复杂度和硬件实现的难度。实验代码通过 Verilog HDL 编写,通过 Modelsim SE 10. 1a 进行仿真,并在 Xilinx Virtex6 XC6VLX760 FPGA 上综合。结果表明,该结构完成  $32 \times 32$  块的预测需要 570 个时钟周期,在 100 MHz 时钟 频率下,可以对 60 f/s,分辨率为  $1920 \times 1080$  的视频帧序列进行实时编码,满足实时性要求。

关键词: HEVC; 帧内预测; 现场可编程门阵列; 硬件加速器

中图分类号: TN919.81 文献标识码: A 国家标准学科分类代码: 460.40

# Hardware implementation of high efficiency video coding(HEVC)intra prediction

Xia Zhengpeng Li Kaiyu

(College of Automation Engineering, Nanjing University of Aeronautics and Astronautics, Nanjing 211106, China)

**Abstract:** In order to meet the real-time requirements, an intra-prediction parallel design architecture based on field programmable gate array (FPGA) is proposed. Through the parallel architecture to reduce the operation latency, through the lookup table to simplify the reference pixel selection process, through the prediction unit to reduce the computation and hardware implementation complexity. The experiment code is written in Verilog HDL, simulated with Modelsim SE 10. 1a, and integrated on the Xilinx Virtex6 XC6VLX760 FPGA. The results show that the prediction of the 32×32 block requires 570 clock cycles. At 100 MHz clock frequency, the video frame sequence with 60 f/s (frame/s) and resolution of 1 920×1 080 can be encoded in real time.

Keywords: HEVC; intra prediction; FPGA; hardware accelerator

#### 0 引 言

HEVC(high efficiency video coding)<sup>[1]</sup>是由视频编码联合组 JCT-VC(joint collaborative team on video coding)在2010年正式提案,并在2013年成为国际标准的新一代视频压缩技术。与 H. 264 相比,在相同视频质量的前提下,HEVC的数据吞吐率达到了两倍以上。

目前,越来越多的应用如视频会议,数字相机依赖于更高分辨率的视频帧以及更加高的帧率,这促使许多研究人员提出了效率更高的算法。文献[2-6]在快速模式选择和CU提前终止划分方面做出了一些改进。然而,软件解决方案的吞吐量不高,不能满足实时性需求,这导致了对于硬件加速器的需求。

Kalali 等人<sup>[7]</sup>基于像素平等的计算减少技术和数据重用技术,提出了一种仅支持 4×4 和 8×8 预测单元大小的

硬件设计。Li等人<sup>[8]</sup>设计了一种 HEVC 帧内预测架构,仅支持 4×4PU 尺寸。它由寄存器阵列和灵活的参考采样选择技术实现,以便显著地减少处理等待时间和寄存器数量。Palomino等人<sup>[9]</sup>提出的架构支持所有帧内预测模式,但是它数据吞吐量低并且需要高频率来处理高分辨率的视频帧序列。Zhou等人<sup>[10]</sup>提出一种 HEVC 帧内预测编码器的流水线 16 像素并行架构,支持所有预测模式和所有尺寸块。该架构完成整个 32×32 尺寸块的帧内预测需要 8 967 个时钟周期。

本文对 HEVC 标准的相关计算公式进行了改进,提出了一种新的并行化硬件设计方案。

#### 1 HEVC 帧内预测

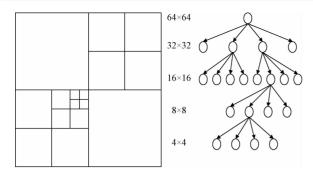

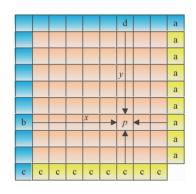

HEVC 帧内预测采用了四叉树的分块结构[11],块的大小可以根据视频内容自适应的改变,如图 1 所示。

图 1 HEVC 四叉树分块方法

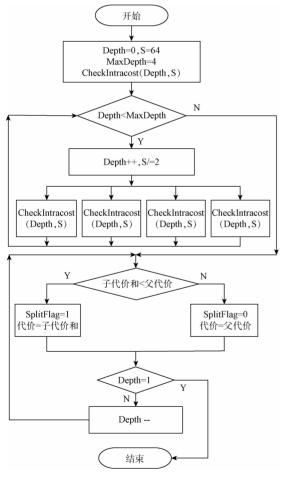

HEVC 帧内预测算法使用相邻预测单元(PU)中的重构像素来预测当前 PU 中的像素。HEVC 帧内预测通过比较当前编码单元(CU)的代价值与其四个子块的代价和的大小来决定最优的模式和块划分方式[12]。预测流程如图 2 所示。

图 2 帧内预测流程

#### 1.1 参考像素替换

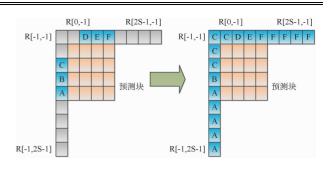

当一部分或者全部参考像素不可用时,需要对不可用的参考像素进行替换<sup>[13]</sup>,如图 3 所示。

#### 1.2 角度预测模式

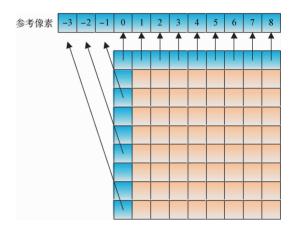

一个像素的预测值取决于当前像素采用的预测方向以

图 3 参考像素替换

及参考像素,预测值为在特定方向上的参考像素投影的线性插值<sup>[14]</sup>,如图 4 所示。

图 4 角度预测模式

考虑预测模式大于等于 18(垂直模式)的情况,预测值可以由以下公式得到:

$$iIdx = ((y+1) \cdot Angle) >> 5 \tag{1}$$

$$iFact = ((y+1) \cdot Angle) \& 31$$

(2)

$predSamples[x][y] = ((32-iFact) \cdot ref[x+iIdx+1] + iFact \cdot ref[x+iIdx+2] + 16) >> 5$  (3) 式中: predSamples[x][y] 表示在  $x,y=1\cdots S-1$  坐标处的预测值,S 表示预测块尺寸,ref[x] 表示实际需要使用的参考像素组。Angle 值与相应的模式有关,如表 1所示。

参考像素组 ref[x] 通过式(4)得到,式中 p[x][y] 表示当前预测块左边和上边相邻 PU 的重构值。

$$ref[x] = p[-1+x][-1], x = 0 \cdots S$$

$$\tag{4}$$

当 Angle 小于 0 时,需要进行参考像素扩展,其中 x = -1···( $S \cdot Angle$ ) >> 5

$$ref[x] =$$

$$p[-1][-1+((x \cdot invAngle + 128) >> 8)]$$

(5)

否则

$$ref[x] = p[-1+x][-1], x = S+1 \cdots 2 \cdot S$$

(6)

invAngle 同样与对应模式相关,对应关系如表 2 所示。

| 表 1 Alight 可模式对应大尔 |     |     |     |     |     |            |    |    |    |    |    |            |            |     |     |     |     |

|--------------------|-----|-----|-----|-----|-----|------------|----|----|----|----|----|------------|------------|-----|-----|-----|-----|

| Mode               | 1   | 2   | 3   | 4   | 5   | 6          | 7  | 8  | 9  | 10 | 11 | 12         | 13         | 14  | 15  | 16  | 17  |

| Angle              | _   | 32  | 26  | 21  | 17  | 13         | 9  | 5  | 2  | 0  | -2 | <b>—</b> 5 | <b>-</b> 9 | -13 | -17 | -21 | -26 |

| Mode               | 18  | 19  | 20  | 21  | 22  | 23         | 24 | 25 | 26 | 27 | 28 | 29         | 30         | 31  | 32  | 33  | 34  |

| Angle              | -32 | -26 | -21 | -17 | -13 | <b>-</b> 9 | -5 | -2 | 0  | 2  | 5  | 9          | 13         | 17  | 21  | 26  | 32  |

### 表 1 Angle 与模式对应关系

#### 表 2 InvAngle 与模式对应关系

| Mode     | 11     | 12    | 13          | 14          | 15          | 16    | 17    | 18   |

|----------|--------|-------|-------------|-------------|-------------|-------|-------|------|

| invAngle | -4 096 | -1638 | <b>-910</b> | <b>-630</b> | -482        | -390  | -315  | -256 |

| Mode     | 19     | 20    | 21          | 22          | 23          | 24    | 25    | 26   |

| invAngle | -315   | -390  | -482        | -630        | <b>-910</b> | -1638 | -4096 |      |

#### 1.3 Planar 和 DC 模式

Planar 和 DC 模式<sup>[15]</sup>主要用于图像平坦区域预测, Planar 模式的预测方法如图 5 所示。

图 5 Planar 预测模式

预测值可以由下式得到:

$$predSamples[x][y] = ((S-1-x) \cdot p[-1][y] + (x+1) \cdot p[S][-1] + (S-1-y) \cdot p[x][-1] + (y+1) \cdot p[-1][S] + S) \gg (\log_2 S + 1)$$

(7)

DC 模式的预测值为左边和上边参考像素的平均值,如下式所示,其中x,y = 0···S - 1,k = log2S.

DCVal =

$$\left(\sum_{x=0}^{S-1} p[x][-1] + \sum_{y=0}^{S-1} p[-1][y] + S\right) \gg (k+1)$$

(8)

#### 2 帧内预测硬件实现

因为 PU 尺寸范围为  $4\times4$  至  $64\times64$ ,且通常  $64\times64$  尺寸的 PU 会被分解为更小的块进行预测,所以本文所支持的预测块尺寸为  $4\times4$  至  $32\times32$ 。

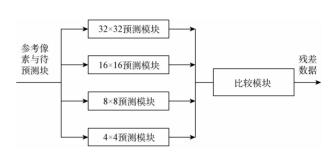

在整个预测过程中,要对每种尺寸的 PU 遍历所有模式来决定最佳的模式和块划分方式。为了避免预测过程中大量的等待时间,本文将预测编码过程分解为 4 条并行处理的过程,如图 6 所示,并在其后增加比较模块以决定最优预测。

图 6 帧内预测并行处理架构

#### 2.1 参考像素选取实现

在进行帧内预测之前,先要为预测准备好相关的参考像素。ref[x]需要使用式(4)、(5)、(6)进行计算,计算过程相当复杂。

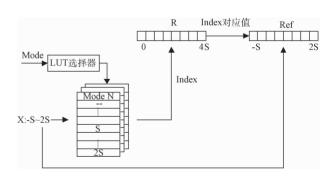

本文提出了如图 7 所示的设计,图中 R 为所有的 4S+1 个参考像素,Ref 为实际预测使用到的参考像素。

图 7 参考像素选取

存储器中为每个预测模式(Mode)设计了一张表,表中的每一项为当前模式需要使用的实际参考像素在 R 中的索引,表项通过事先计算得到。帧间预测开始之前,预测器以 Mode 作为输入,LUT 选择器根据当前 Mode 选中相应的表并使能。表以 X 为索引,取出表项中预先存储的参考像素在 R 中的索引值 Index。 R 以 Index 为索引,取出表项的值,构成实际预测需要的参考像素组 Ref。

#### 2.2 角度模式实现

通过分析可以发现,在垂直模式中,iFact与iIdx的 值在一行中保持不变。同样,在水平模式中,iFact与iIdx的值在一列中保持不变。

本文事先为每个模式计算好当 x 或 y 为 0~31 时所 对应的 iFact 与 iIdx 的值并以表的形式存储在内存中,待 需要使用时再查表取出。

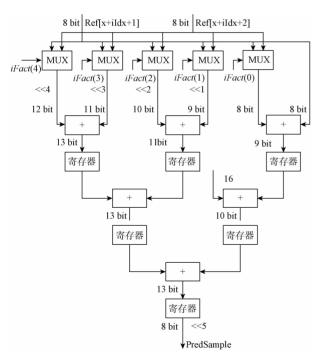

式(3)根据 iFact、iIdx 和 ref[x] 进行帧内预测,预测 过程中需要进行复杂的乘法运算。通过仔细研究,本文对 式(3)进行了改写,改写形式如式(9)所示,式中 not(iFact)为 iFact 讲行 5 bit 取反。

$$predSamples[x][y] =$$

$$(not(iFact) \cdot ref[x + iIdx + 1] +$$

$$iFact \cdot ref[x + iIdx + 2] +$$

$$ref[x + iIdx + 1] + 16) \gg 5$$

(9)

根据改写后的式(9),本文设计提出了如图 8 所示的 运算单元。此运算单元由5个多路选择器,数个加法运算 单元以及若干移位寄存器组成,避免了预测过程中大量的 乘法运算,而改为更为简单的加法和移位运算,多级的流 水线结构使运算更加高效。

图 8 预测运算单元

多路选择器以 iFact 的每一位作为选择因子, ref[x+iIdx + 1 和 ref[x + iIdx + 2] 为输入。

#### 2.3 Planar 和 DC 模式实现

Planar 模式的处理与角度模式处理相似。式(7)中 S 因为预测块尺寸的不同而不同,所以对于 4 条并行线路各 有不同的设计结构。以  $8\times8$  块举例,此时 S=8,式(7)可

改写为:

$$predSamples[x][y] = (not(x) \cdot p[-1][y] + x \cdot p[8][-1] + not(y) \cdot p[x][-1] + y \cdot p[-1][8] + p[8][-1] + 8) \gg 4 \quad (10)$$

由式(10)可以看出,Planar模式的预测运算单元与角 度模式预测运算单元类似,由于式(10)同时存在x和v两 个变量,所以需要两个相同的运算结构组合来得到最后的 结果。

DC 模式仅需要当前 CU 参考像素值相加并移位即 可,当前CU参考像素来源于其上边和左边相邻PU的重 构值。

#### 3 实验及结果分析

本文设计的帧内预测系统支持 32×32、16×16、8×8 和 4×4 尺寸的预测块进行预测。为了验证设计的准确性 和可行性,对相同数据块和参考像素,本文将官方测试模 型 HM10.0 所产生的结果与本文所设计结构的仿真结果 讲行比较。

待预测块与其参考像素作为输入提供给 HM10.0 以 及本文所设计硬件模块,对硬件模块使用 Modelsim SE 10.1a 进行仿真验证。本文将两者输出进行比较,其运行 结果保持一致,证明了本文设计模块的正确性。

本文使用 Xilinx 公司 Virtex6 系列的 XC6VLX760 对 所设计模块进行综合。综合结果显示,本文设计模块占用 156 K LUT 和 121 K 寄存器资源,各个尺寸 CU 占用资源 及完成预测所需的时钟周期如表 3 所示。

PU尺寸 时钟周期 资源占用 10.6 K LUT, 8.3 K REG  $4 \times 4$ 25  $8 \times 8$ 22.3 K LUT, 20.1 K REG 48  $16 \times 16$ 160 40.9 K LUT, 38.5 K REG

82.2 K LUT, 54.1 K REG

表 3 不同 PU 尺寸占用资源情况

由仿真实验得出,完整的预测完 32×32 尺寸块仅需 要 570 个时钟周期。对于主频为 100 MHz 的处理器而言, 对 1 帧 832×480 分辨率的图像进行编码仅需要 0.002 s, 可以对 60 f/s,分辨率为 1 920×1 080 的视频帧序列进行 实时编码。本文所设计结构可以达到很高的数据吞吐量, 完全能满足实时性要求。

570

#### 4 结 论

$32 \times 32$

本文提出了一种并行化处理的帧内预测模块硬件架 构,该设计支持所有的预测模式以及所有的 PU 尺寸。本 文还对帧内预测运算单元进行了简化设计,通过对预测公 式进行适当的变换,将复杂的乘法运算变换为利用多路选 择器,加法器以及移位寄存器实现的简单结构。仿真结果 显示,本文所设计模块可以对 60 f/s,分辨率为 1 920× 1 080的视频帧序列进行实时编码,满足实时性要求。

#### 参考文献

- [1] 卢鑫,林茂六,金雪松,等.新一代可伸缩视频编码标准:背景、特征、技术及其应用[J].电子测量与仪器学报,2015,29(10):1415-1423.

- [3] 赵爽,陈敬东,陈敏. 一种 HEVC 帧内预测模式快速选择算法[J]. 计算机与数字工程,2016,44(10): 1992-1995.

- [4] 詹晓涛. HEVC 帧内预测编码快速判决算法分析[J]. 中国有线电视, 2015(7):823-828.

- [5] 梅健,谢林柏. 基于 HEVC 的帧内预测模式快速选择算法[J]. 计算机工程与应用,2016,52(10):187-191.

- [6] 伍冠健, 宋立锋. HEVC 快速帧内模式和深度决策 算法「J」. 广东工业大学学报, 2015, 32(4):132-137.

- [7] KALALI E, ADIBELLI Y, HAMZAOGLU I. A high performance and low energy intra prediction hardware for high efficiency video coding [C]. International Conference on Field Programmable Logic and Applications. IEEE, 2012;719-722.

- [8] LIF, SHIG, WUF. An efficient VLSI architecture for 4×4 intra prediction in the high efficiency video coding (HEVC) standard [C]. IEEE International Conference on Image Processing, IEEE, 2011;

373-376.

- [9] PALOMINO D, SAMPAIO F, AGOSTINI L, et al. A memory aware and multiplierless VLSI architecture for the complete intra prediction of the HEVC emerging standard [ C ]. IEEE International Conference on Image Processing, IEEE, 2012; 201-204.

- [10] ZHOU N, DING D, YU L. On hardware architecture and processing order of HEVC intra prediction module [C]. Picture Coding Symposium, IEEE, 2013;101-104.

- [11] 赵耀,黄晗,林春雨,等. 新一代视频编码标准 HEVC 的关键技术[J]. 数据采集与处理,2014(29):1-10.

- [12] 周作成, 贾克斌. 新一代视频编码标准 HEVC 关键技术及其应用[J]. 北京工业大学学报, 2014, 40(10):1489-1496.

- [13] 唐顺峰,王蕾.基于 HEVC 标准视频框架下帧内预测技术的研究[J]. 电子质量,2015(1):56-59.

- [14] 朱秀昌,李欣,陈杰.新一代视频编码标准——HEVC[J].南京邮电大学学报:自然科学版,2013,33(3):1-11.

- [15] 谢晓燕,徐卫芳,刘帆. HEVC 帧内预测 Planar 和 DC 模式算法的并行化设计[J]. 电视技术,2015,39(5):4-8.

#### 作者简介

**夏正鹏**,工学硕士,主要研究方向为计算机测控。 E-mail:nuaa\_xzp@163.com