DOI:10. 19651/j.cnki.emt.2105771

# 基于光学时钟技术的高速 ADC 系统的研究\*

#### 吕方兴

(安康学院 电子与信息工程学院 安康 725000)

摘 要:时间交替模数转换器(time-interleaved analog-to-digital converter, TIADC)是一种有效地提高模数转换器采样频率的方法,但是通道间的采样时间相对误差严重影响了系统性能。基于光学时钟技术的高速 ADC 技术主要是利用光脉冲信号的高重频、窄脉宽和低时间抖动特性。提出了一种基于光学时钟技术的 TIADC 系统的设计方案,利用不同的光纤长度产生精准时间间隔的采样信号,并通过搭建一个四通道 TIADC 来验证方案的可行性。实验结果表明,该光时钟分配系统可以提供小于 16~ps 的四通道时钟信号,能够很好地实现四通道高速 ADC 系统。

关键词: 高速 ADC;时间交替采样;光纤延时线;光学时钟技术;时间抖动

中图分类号: TN29; TN929 文献标识码: A 国家标准学科分类代码: 510.20

# Photonic time-interleaved ADC based on optical clock distribution

Lyu Fangxing

(School of Electronic and Information Engineering, Ankang University, Ankang 725000, China)

Abstract: Time-interleaved analog-to-digital converter(TIADC) is an effective way to increase the sampling frequency of ADC, but the sampling time and relative error between the channels seriously affect the system performance. Proposed a photonic time-interleaved analog-to-digital conversion (TIADC) scheme by exploring optical clock distribution. A proof-of-concept experiment with a four-channel TIADC was implemented and demonstrated. Experimental results show that the optical clock distribution system can offer a four-channel clock with low jitter. These results are very encouraging toward the development of optical clock distribution based electrical systems in the practical applications. Keywords: high-speed analog-to-digital conversion; time interleaving; optical delay line; optical clock distribution; timing jitter

# 0 引 言

作为连接模拟系统与数字系统的枢纽,模数转换器(analog-to-digital converter, ADC)的地位与作用日益突出[1-3]。随着现代社会进入高度信息化时代,所需处理的信号带宽成倍增长,各种应用对模数转换技术的要求也越来越高。特别是在雷电冲击测试、超宽带通信、软件无线电、电子战等应用领域,对模数转换技术的采样速率等提出了更高的要求[1-7]。

传统电子 ADC 技术由于载流子迁移速率受限、热噪声等因素的影响,其性能受到了极大地限制[8-10]。随着光学技术的迅速发展,利用光学手段来突破电子 ADC 的瓶颈问题,实现超高速、高精度模数转换已经成为高速 ADC 领域的一个研究热点[11-13]。浙江大学池灏教授团队[14]通过对

电光调制器阵列施加不同的直流偏置来改变其输出光强,实现了 4 bits 的量化精度。但是,采用这种方法要获取高的量化精度,必须集成较多的电光调制器,且调制器的半波电压要降到很低。美国加州大学圣地亚哥分校 Esman 等[15]于 2014 年采用基于光纤四波混频效应的全光采样门,实现了 100 GS/s 采样率、6 bits 量化精度的模数转换性能。但是由于光采样过程中增益不一致以及分路时间难以精确控制等问题,该方法的量化精度还是难以达到人们所期待的精度。

本文提出了一种基于光学时钟的多路并行时间交替采样 ADC 系统,该系统不仅可以提高电子 ADC 的采样速率为单个 ADC 采样速率的 N 倍 (N 为并行 ADC 的个数),改善电子时钟信号延时不准确、时间抖动、重复频率低等问题,而且充分利用了电子 ADC 转换精度高的优势。在本文

收稿日期:2021-01-30

<sup>\*</sup>基金项目:陕西省教育厅项目(20JK0478)、校级青年基金项目(2019AYQJ01)、陕西省高等教育教学改革研究重点项目(19BZ057)、陕西省教育科学"十三五"规划项目(SGH20Y1347)、国家创新创业训练计划项目(S202011397012)、陕西省创新创业训练计划项目(S202011397081)资助

提出的高速采样系统中,由较成熟的电子 ADC 芯片构建多路并行采样量化电路,采用稳定性好、定时抖动小的光学脉冲为每路 ADC 芯片提供时钟信号,利用光学延时技术获得多路时钟之间的精确相位延时,通过 FPGA 实现多路并行ADC 的数据读取与缓存。本文详细介绍了系统结构,光时钟产生与延时方法,硬件电路的设计,并通过实验验证了系统可行性。

# 1 系统的工作原理

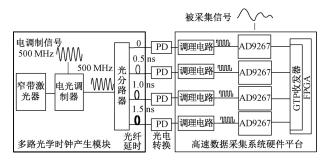

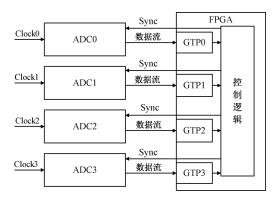

图 1 以基于光学时钟的 4 路并行高速 ADC 系统为例 说明分时交替采样的工作原理。在该系统中,光学时钟发生模块产生光学时钟信号;然后经光分路器均分成 4 路并行光学时钟信号;为了能达到分时交替采样的目的,4 路光学时钟信号分别通过不同长度的光纤延时线进行延时;延时后的光学时钟信号再通过光电转换及处理模块转换成合适的电时钟信号;最后由该光电时钟信号触发电子 ADC 完成数据采集与量化,并通过 FPGA 模块完成数据读取和级存。从功能上来看,高速数据采集系统主要由多路光学时钟发生单元和电子模数转换及数据处理单元构成。其中多路并行的光学时钟是本文设计的高速数据采集系统的主要特色。相比电学时钟,光学时钟在光电转换之前进行的光学时钟分路、精确的时钟相位延时、抗电磁干扰等方面具有明显的优势。

图 1 4 路并行高速 ADC 系统的结构框图

假设单路 ADC 的采样周期为  $T_s$ ,采样率为  $f_s$ ,并且在时钟的上升沿采样。为实现交替采样,则每路的采样时钟需要相对前一路的采样时钟延时  $T_s/4$ ,即其他 3 路相对于第 1 路分别延时  $T_s/4$ ,2  $T_s/4$  和 3  $T_s/4$ 。

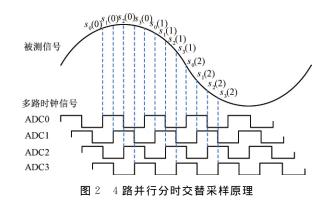

图 2 为延时之后的各路时钟波形。每一路的电子 ADC 会在各自时钟的上升沿对被测信号进行采样。虽然单独来看每路 ADC 的采样周期仍然是  $T_s$ ,但由于各路之间存在相位延迟,从整体来看,系统对被测信号采样 4 次,从而使最终的采样间隔变为  $T_s/4$ 。最后在数字域合成采样结果,就能够实现  $4f_s$ 采样率的模数转换。设第 i 个 ADC 的第 k 个采样点为  $s_i(k)$ ,则最终得到的采样序列为:

$$s = [s_0(0), s_1(0), s_2(0), s_3(0), \dots, s_0(k), s_1(k), s_2(k), s_3(k)]$$

(1)

# 2 光学时钟信号的产生及时序分配技术

传统的电学时钟是通过恒温晶振和多级锁相环来产生的,易引入噪声,时钟抖动较大。此外,电路延时技术延时精度不高,并且在电路延时过程中需要考虑到信号完整性、电磁兼容、PCB加工工艺等因素的影响。因而,在通道数较多或超高速的交替采样中,电学多路时钟根本无法保证精度。为解决这种电学时钟抖动和延时过程中的问题,采用了光学时钟源及光学分路、延时和时序分配技术。

#### 2.1 基于电光调制方法的光学时钟信号发生技术

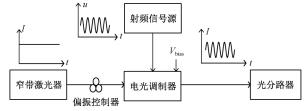

基于电光调制技术生成高频光学时钟信号的实现原理 如图 3 所示。

图 3 电光调制法获得光学时钟原理

窄带激光器发出的准单色连续光信号(中心波长为1550 nm,光谱线宽小于15 pm,平均功率为20 mW),经偏振控制器输入到电光强度调制器中。实验中电光强度调制器工作带宽10 GHz,插入损耗为5.5 dB,偏置电压设置在正交点(4.1 V),线偏振光输入。电调制信号为正弦波,由射频信号发生器提供。在电光调制器中,连续光的光强受到高频正弦电信号的调制,从而转换为与电调制信号同频的正弦信号,即光时钟信号。在该方案中,所产生光时钟信号的重复频率可以通过调节电调制信号的频率来改变,这为光时钟系统驱动不同采样频率的电子ADC提供了方便。

#### 2.2 光学时钟信号的精确延时和时序分配技术

对于光时钟信号,很容易采用光学分路器、光纤延时线等光学无源器件实现时钟信号的分路与精确延时,而不会引入额外的噪声。另外,还可通过光纤延时线实现时钟信号的远距离传输,并且传输过程中抗干扰能力好。

#### 1) 光时钟信号的精确延时技术

光纤延时线主要通过控制光纤的物理长度来实现时钟

• 18 •

信号的延时,也是最简单方便的一种光学延时方法。相比于传统的电学延时,光学延时能够避免"电子瓶颈"问题,具有带宽大、精度高、结构简单、抗电磁干扰等特点。

根据光纤传输理论,当一束准单色光信号通过长度为L的光纤后,产生的延迟时间可表示为:

$$\tau = \frac{L}{\tau} = \frac{L \cdot n}{c} \tag{2}$$

其中,n 为光纤在该中心波长处的折射率,v 为光在光纤中的传播速度,c 为真空中的光速。对于特定的波长和光纤介质,折射率 n 与真空中的光速 c 为定值。由式(2)可知,延时时间与光纤延时线的长度 L 成正比,因此,通过改变光纤的长度就能够改变时钟信号的延迟时间。

采用的光纤延时线为康宁公司提供的普通单模光纤 (SMF-28),在波长 1550 nm 处的折射率为 1.4682,那么通过计算可得单位长度 (1m) 光纤产生的延时时间约为 4.89 ns.

由式(2)可知,如果延迟光纤的长度控制精度为 $1 \, \mathrm{mm}$ ,对应的延时时间为 $5 \, \mathrm{ps}$ 。这意味着在高速多路并行 ADC 系统中,如果相邻两路 ADC 的时钟信号延时时间可以精确控制在 $5 \, \mathrm{ps}$ ,理想情况下,最终获得的多路合并时钟信号的最高等效频率将可以达到 $200 \, \mathrm{GHz}$ 。

#### 2) 光时钟信号的时序分配技术

本文提出首先生成光时钟信号,然后采用光学分路器实现对光时钟信号的分路,从而获得多路时钟信号。每一路光时钟信号通过不同长度光纤延时线进行延时,实现多路时钟的时序分配。最后将光时钟信号转换为电时钟信号,并经过整形电路后分别供给每路的 ADC 芯片,作为其时钟信号。

与多路电时钟相比,多路光时钟的时序分配过程具有以下优点:(1)时钟信号在光纤或光波导介质中传输,电磁兼容性好;(2)分路与延时不会引入额外的抖动与带宽限制;(3)延时分辨率高(5 ps),并且通过改变光纤延时线长度可以很方便地调节多路时钟的时序,补偿光电转换、高频线路及电子元件引入的不匹配延迟;(4)可扩展性好。采用级联方式或者选择多通道输出的光分路器增加时钟输出通道数量,同时改变每个通道接入光纤延时线的长度,即可实现更高等效频率的光电时钟,后端只需并联更多 ADC 模块即可实现高速 ADC 系统的扩展。该扩展工艺简单、成本低。

#### 2.3 高速光电转换及整形调理电路的设计

基于光学时钟的多路并行交替采样 ADC 系统中,采样和量化过程由电子 ADC 完成。因此,光学时钟信号最终要转换成电时钟信号,输入到电子 ADC 的采样同步时钟输入端口。光电转换模块是光路与电路的结合点,其核心是光电探测器。光电探测器将输入光强转换成电流信号,电流信号再经前置放大电路放大的同时转换成电压信号输出。其中光电探测器选择的是北京康冠光电公司 KG-PR-10G-A

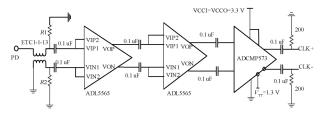

型的光电转换模块。该光电探测模块集成了高速 PIN 探测器和低噪声放大器,具有高增益、高灵敏度等特点。其主要参数有:响应光谱范围为  $800\sim1~700~\mathrm{nm}$ ,典型值为  $1~550~\mathrm{nm}$ ;光敏面直径为  $0.~2~\mathrm{mm}$ ;3 dB 带宽为  $10~\mathrm{GHz}$ ;饱 和光功率为  $4.~7~\mathrm{mW}$ 。由于光电转换模块输出的是幅值较小的单端电压信号,必须经过放大整形处理才能用于触发高速电子 ADC 进行采样。时钟调理电路的原理如图  $4~\mathrm{fm}$ 示。

图 4 时钟调理电路原理

光电转换模块输出的单端电压信号由阻抗比为 1:1 的传输线变压器转换为差分信号。ADL5565 实现高频差分信号的两级放大。为了保证电子 ADC 在时钟信号的上升沿有比较准确的采样触发时间,本文采用超快型电压比较器 ADCMP573 对时钟信号做进一步整形处理,实现差分方波信号的输出。比较器输出的差分方波信号具有 PECL逻辑电平,可以与 ADC 芯片实现直流耦合或交流耦合的互连。

时钟调理电路包括放大和比较器整形两部分,显然,它们会对输入的时钟信号产生附加的延时和抖动。为了最大程度的限制调理电路带来的影响,设计中需充分考虑到高频信号传输过程中的信号完整性和电磁兼容特性两个关键问题,合理设计相关电路及印制电路板。

# 2.4 ADC与 FPGA 互连的接口设计

ADC 和 FPGA 之间的连接主要是串行数据传输总线和同步信号 Sync 控制逻辑总线,设计的结构框图如图 5 所示。所选用的 ADC 芯片 (AD9267)的数据输出端口与GTP 收发器的接收端口具有相同的逻辑电平,可以通过直流或交流进行耦合连接;Sync 端口与 FPGA 的普通 IO 口直接相连。

#### 3 光电时钟性能测试的实验研究

#### 3.1 时钟调理电路输出信号实验结果与分析

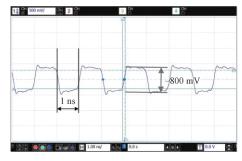

调制电信号由射频信号源(DSG3030)给出,其输出频率范围为 9 kHz  $\sim$  3 GHz。采用安捷伦示波器(MSO9254A,带宽2.5 GHz,采样速率20 GSPS)及其附件高频差分探头(带宽为3.5 GHz)检测调理电路输出的时钟波形,测试结果如图6所示。

从图 6 中可以看出,调理电路输出的差分时钟信号的 峰峰值约为 800~mV 左右,满足一般 ADC 芯片对时钟信号 幅值  $(0.2\sim6~V)$  的要求。时钟信号的上升时间小于

图 5 AD9267 与 FPGA 互连的结构框图

图 6 调制信号频率 500 MHz 时钟调理电路波形

200 ps,可满足采样速率最大约为 1 GHz 的 ADC 芯片对时钟信号的要求。此外,通过实验观测在不同频率的调制电信号下 $(0,1\sim1,2$  GHz)时钟调理电路输出的电时钟信号波形,可以知道光电时钟系统输出的电时钟信号的最高频率可达到 1 GHz。最高频率主要受限于时钟信号调理电路的传输带宽。本文提出的基于电光调制法的时钟信号发生方案中,光路部分带宽受限的器件主要有射频信号源(输出信号最高频率为 3 GHz),电光调制器和光电探测器(两者带宽均为 10 GHz)。当不考虑电路部分的影响时,单路光学时钟的最高频率可达到 3 GHz。

综合光路与电路部分的带宽限制,光电时钟发生装置的单路最高时钟频率可达  $1~\mathrm{GHz}$ 。理论上,采用  $1~\mathrm{O}$   $10~\mathrm{O}$  的光分路器结合光纤延时线在每路光时钟信号引入  $100~\mathrm{ps}$  (相当于光纤长度差约为  $2~\mathrm{cm}$ ,易于实现)的延时,因此本文设计的光电时钟发生装置最高可以实现  $10~\mathrm{GHz}$  的时钟信号。为了验证验证该方案的可行性,本文采用了  $4~\mathrm{B}$   $500~\mathrm{MSPS}$  采样速率的  $\mathrm{ADC}$  芯片( $\mathrm{AD9267}$ )组建系统。

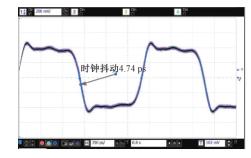

#### 3.2 时钟信号时间抖动性能的测试结果与分析

时钟抖动的来源包括射频信号源、调理电路、示波器、及其由光学部分引入的抖动。基于电光调制方法的时钟信号产生装置中,时钟信号的抖动主要来自于电学处理电路。本文对整个光电时钟系统输出的时钟信号的抖动进行了实验观测。其结果如图 7 所示。由图 7 中可以看出,调制信号频率为 500 MHz 时光电时钟时间抖动均方根值为4 7 ps,满足工程上对 10 GHz 时钟信号的时间抖动的要求(时间抖动应小于时钟周期的 1/5)。

图 7 调制信号频率 500 MHz 时钟信号的时间抖动波形

#### 3.3 光纤延时及时序分配结果与分析

由于各通道的光电探测模块和调理电路并非完全一致,因此多路电时钟信号存在固有的相位延迟差。各通道的电路相移对于同频率的时钟信号来说是固定的,因此电路产生的相位延时并不影响光学时钟错相及时序分配。

在此基础上设计 4 路时钟信号发生装置: 光学时钟由 光纤耦合器分为 4 路时钟信号, 每路时钟信号接入不同长 度的光纤实现预期的相位延时, 每路时钟信号频率为 500 MHz。此时调理电路输出方波信号,以通道 1 为参考, 其他三通道与之时序差依次为 0.5、1.0 和 1.5 ns,即相邻 两路之间的时序差为 0.5 ns,满足时序分配设计的要求。 另外,实验证实通过改变光纤延时线长度可以很方便的调 节时钟通道间的时序差,补偿光电转换、高频线路及电子元 件等引入的不匹配延迟。

# 3.4 系统实验结果及分析

本文测试了在输入不同频率的射频信号时,高速 ADC 系统的性能。当输入的正弦波信号频率分别为 50 和 200 MHz时,使用 MATLAB 对 FPGA 的 ChipScope 模块保存的 4 路数据进行时间交替整合处理得到波形如图 8 所示。其中黑点符号代表来自 4 路 ADC 的采样点合成后的数据,黑色曲线表示经过最小二乘法拟合后得到的正弦信号。

从图 8 中可以看出,对应信号频率 50 和 200 MHz,信号单周期内系统整体采样点数分别为 40 点和 10 点,这表明系统整体采样率达到 2 GSPS。衡量一个模数转换系统转换精度最典型的参数是其信噪失真比与由信噪失真比得到的有效位数。信噪失真比是信号功率的均方根与噪声和失真的均方根之比,与系统的采样速率、信号幅度、信号噪声、谐波失真、噪声等均有非常密切的关系。IEEE 标准<sup>[8]</sup>提供了一个计算信噪失真比的方法,由下式给出:

$$SINAD = \frac{A_{\text{rms}}}{\sqrt{\frac{1}{M} \sum_{n=1}^{M} (x [n] - x' [n])^2}}$$

(3)

式中:SINAD 表示系统的信噪失真比,单位为 dB;A<sub>rms</sub>表示根据系统采样点求出的拟合曲线幅值的均方根值;x[n]代表采样点的数值;x'[n]代表拟合曲线的数值;M 代表采样点的个数。

• 20 •

图 8 分时采样 ADC 系统采样数据恢复的波形图

系统的有效位数(ENOB)可通过信噪失真比(SINAD)进行计算,公式如下:

$$ENOB = \frac{SINAD - 1.76}{6.02}$$

(4)

系统输入不同频率正弦信号时,信噪失真比和有效位数的计算结果如表1所示。

表 1 实验得到不同信号频率的信噪失真比及有效位数

| 输入信号频率/MHz          | 50     | 100    | 200         |

|---------------------|--------|--------|-------------|

| SINAD/dB            | 57. 35 | 37. 90 | 24. 04      |

| $ENOB/\mathrm{bit}$ | 11. 0  | 9. 2   | <b>6.</b> 0 |

由表 1 可以看出,输入信号频率较低时,系统有效位数非常接近电子 ADC 的量化位数。但随着射频信号频率的增加,系统信号噪声失真比和有效位数呈下降趋势。该现象可以解释为,当输入信号频率增加时,由热噪声、采样孔径抖动以及比较器不确定性引起的有效位数下降。

由此可知,系统实现了多路光学时钟的设计,结果表明:采用电光调制方法获得频率可调的光学时钟源是可行的;光电时钟单路可实现的最高频率为1 GHz,时钟抖动小于16 ps,延时精度可达5 ps;光分路器输出通道数量可达几十上百。理论上该光学时钟发生装置可以实现数十 GHz 的高速 ADC。因此本文提出的多路光学时钟方案,能够用于ADC系统的采样时钟。与传统的多路电学时钟相比,它具有可扩展性好、便于补偿多路时钟相位不匹配延迟的优点。

# 4 结 论

本文提出的基于光学时钟技术的高速 ADC 技术的核心思路是利用光脉冲重复频率高、抖动小、延时精确等特点,替代传统的电时钟信号去触发电子 ADC 采样。本文产生的多路光时钟信号的时间间隔可精确控制,结合多路时分电子 ADC 技术,实现了基于光学时钟技术的 4 路并行高速 ADC 系统。为了验证该方案的可行性,搭建了基于光学时钟的 4 路并行采样的模数转换硬件平台,该平台以高速模数转换芯片 AD9267 为采样、量化的核心,采用 FPGA 高速串行接收模块 GTP 收发器完成线速率高达 6 Gbps 的数据通信,最终实现了采样率 2 GSPS 量化位数为 12 位的高速 ADC 系统。

由于光时钟信号非常易于分路,且不会产生电时钟信号分路过程中抖动、延时等问题,因此该技术可由芯片级扩展形成板级 ADC 系统。该方案存在的主要问题是系统体积庞大、集成化程度较低。下一步,将进行光学时钟信号的小型化、稳定性方面的研究,从而减小系统的体积。

#### 参考文献

- [1] NAGASHIMA T, HASEGAWA M, KONISHI T. 40 GSample/s all-optical analog to digital conversion with resolution degradation prevention [J]. IEEE Photonics Technology Letters, 2016, 29(99):74-77.

- [2] 郝少帅,杨玉华,王淑琴.基于 FPGA 的高精度采集系统的研究与实现[J].电子测量技术,2020,43(19):

- [3] 李美花, 闫卫平, 王颖, 等. 微传感器阵列多通道数据 采集和处理系统[J]. 电子测量与仪器学报, 2016, 30(2);311-317.

- [4] 赵计贺,李杰,张德彪,等.弹载飞行参数高精度采集系统设计[J].中国测试,2020,46(12):73-78,104.

- [5] RAUTH D A, RANDAL V T. Analog-to-digital conversion-Part 5 in a series of tutorials in instrumentation and measurement [J]. IEEE Instrumentation & Measurement Magazine, 2005, 8(4): 44-54.

- [6] 崔琪, 顾金良, 刘庆国,等. 基于 DSP+FPGA 的高速数据采集系统的设计[J]. 国外电子测量技术, 2020, 39(1):99-104.

- [7] 张雪皎,陈剑云.基于 ZYNQ 的高速数据采集系统设计 [J].华东交通大学学报,2020,37(6):119-125.

- [8] 胡梅,李晓宇,陈建云.采样噪声对北斗全球信号测距 误差的影响分析[J].仪器仪表学报,2019,40(9): 180-188.

- [9] XU D, JIANG H, FU D, et al. A linearity improved 10 bit 120 MS/s 1. 5 mW SAR ADC with high-speed and low-noise dynamic comparator technique [J]. Journal of Circuits, Systems and Computers, 2020,

- 29(6):2808-2812.

- [10] SEYED Z, MARVIN O. Review of analog-to-digital conversion characteristics and design considerations for the creation of power-efficient hybrid data converters [J]. Journal of Low Power Electronics and Applications, 2018, 8(2):12.

- [11] WU Z, LYU F, DING H. A promising optoelectronic clock solution to time-interleaved ADC [ J ]. International Journal on Smart Sensing and Intelligent Systems, 2020, 7(5):1-4.

- [12] WEBER S, WALLER E H, KAISER C, et al. Time-stretched real-time measurement technique for ultrafast absorption variations with TS/s sampling-rate [J]. Optics Express, 2017, 25(13): 14125-14133.

- [13] GENG X, ZHAO L. All-optical analog to digital

- converter based on nonlinear photonic crystal ring resonators [ J ]. Photonics and Nanostructures-Fundamentals and Applications, 2020, 41:100817.

- [14] HE H, CHI H, YU X, et al. An improved photonic analog-to-digital conversion scheme using Mach-Zehnder modulators with identical half-wave voltages [J]. Optics Communications, 2018, 425; 157-160.

- [15] ESMAN D J, WIBERG A O J, YANG M H, et al. Photonic parametric sampled analog-to-digital conversion at 100 GHz and 6 ENOBs[C]. European Conference on Optical Communication, IEEE, 2014: 1-3.

#### 作者简介

吕方兴,工学博士,讲师,主要研究方向为光纤传感技术、 高速光学 ADC 技术等。

E-mail:lfx85ilu@126.com